#### Recommendations and Roadmap for European Sovereignty in Open Source Hardware, Software, and RISC-V Technologies

Report from the

Open Source Hardware & Software Working Group

November 2021

#### Members of the Open Source HW/SW Working Group

• Chair:

Patrick Pype NXP Semiconductors

• Participants :

Jan Andersson Cobham Gaisler

Luca Benini ETH Zürich / Univ. Bologna

Sven Beyer Siemens

Holger Blasum SYSGO GmbH

Sylvain Depierre NanoXplore

Marc Duranton CEA

Wolfgang Ecker Infineon

Michael Gielda Antmicro Ltd

Edwin Hakkennes Technolution

Andreas Koch Technische Universität Darmstadt

Loic Lietar GreenWaves Technologies

Andreas Mauderer Bosch

Jan-Hendrik Oetjens Bosch

Jérôme Quévremont Thales

John Round NXP Semiconductors

Javier Serrano CERN

Herbert Taucher Siemens

### . What is RISC-V?

- Open standard instruction set architecture

- Provided under open-source licenses with no fees to use

- Initially designed for academic use and educational purposes

- Is the starting point for designing a HW processor in a certain process technology

- "RISC-V International" owns, maintains and publishes IP related to RISC-V only specification, no implementation

# RISC-V IP to SoC landscape

**Base Building Blocks**

High-end RISC-V core

Mid-end RISC-V core

Low-end RISC-V core

Other SoC IPs

(interconnect, peripherals...)

#### Software

(OS, tool chains, compilers, drivers, debuggers...

Domain-specific features (safety, security, acceleration, Al...)

**Custom RISC-V extensions**

Co-processors / accelerators

Customized solutions for various markets

Automotive

Industrial

Communication

**HPC**

Other sectors

- Standard extensions

- Custom extensions

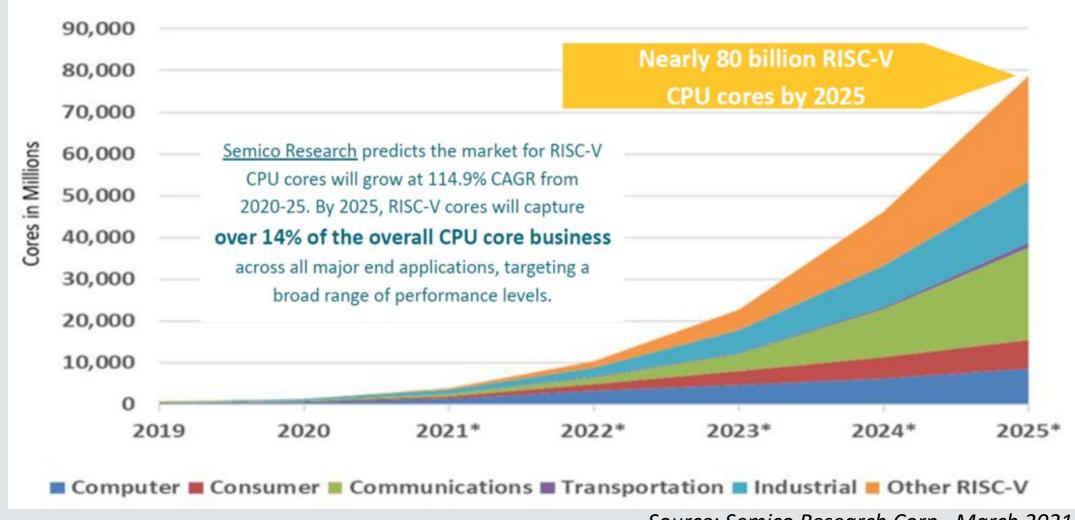

# RISC-V Usage

Source: Semico Research Corp., March 2021

"23% of projects in both the ASIC and FPGA spaces incorporated at least one RISC-V processor."

(Source: Wilson Research Group Functional Verification, 2020)

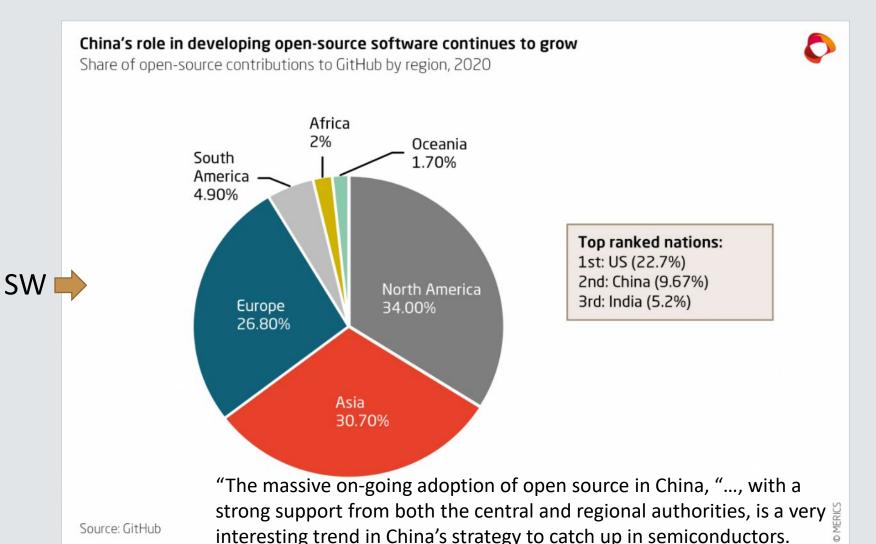

# Open Source in China

"Alibaba introduced first RISC-V based product (XT910) in July 2020"

(Source: https://www.nextplatform.com/2020/08/21/alibaba-on-the-bleeding-edge-of-risc-v-with-xt910/)

interesting trend in China's strategy to catch up in semiconductors.

"For China, open source is an industrial policy tool and important part of its push for technological autonomy"

#### Source:

https://merics.org/en/shortanalysis/china-bets-opensource-technologies boostdomestic-innovation

Source: GitHub

# Why RISC-V in Europe?

#### **STRENGTHS**

- Easy access & low barrier for SoC design

- Ability to customize

- Accessible data for safety & security analysis (whitebox)

- Availability of SW ecosystem

- Lower export control restrictions

- Less vulnerable to geo-political risks

- Strong academic support; educational use

- Steers Innovation

#### **OPPORTUNITIES**

- Customization opportunities

- Sharing development costs

- Sharing support costs

- New licensing models

- Support to SME's

- New industrial leaders

#### **WEAKNESSES**

- Not Industrial Quality IP yet (HW/SW)

- Long-term guaranteed support to industrial users not yet established

- Risk of maintenance

- Lack of some IP (e.g. interconnect)

#### **THREATS**

- Risk not to create enough critical mass in Europe

- US/China competitors are running fast, with large investments and acceptance by leading end-user companies

Europe must

develop

the RISC-V supply

chain to support

autonomy in critical

market sectors and

reduce its

dependency

on US & China

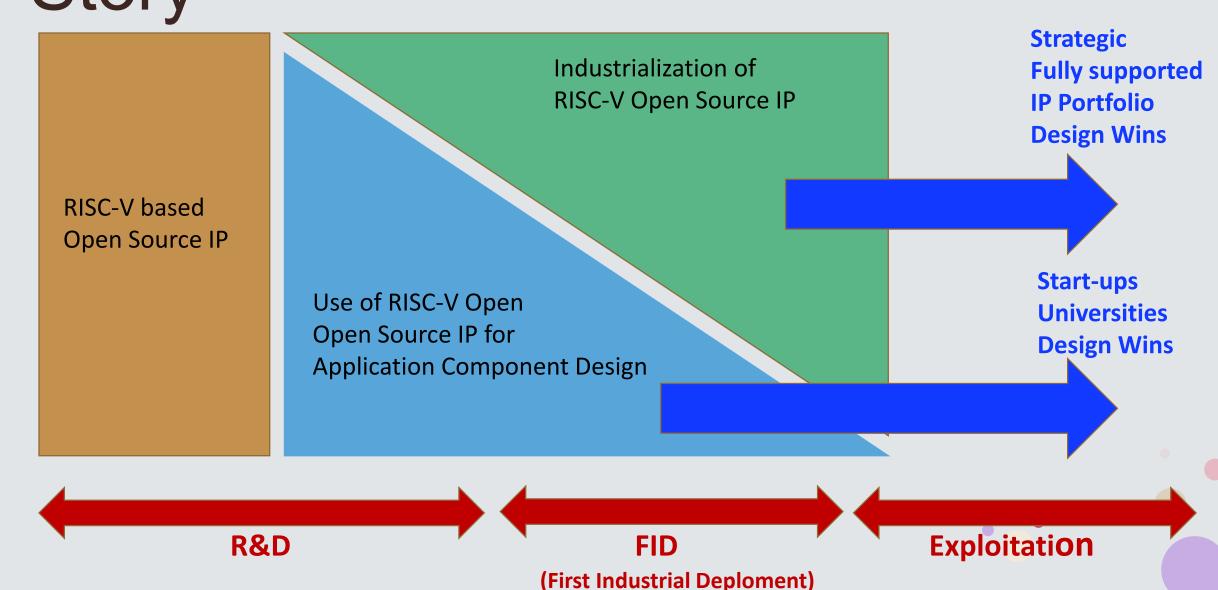

# Approach to European Success Story

# Approach to European Success

. Story **Closed IP** "Airbus **Strategic** of Industrialization of **Fully supported** RISC-V" RISC-V Open Source IP **IP Portfolio** or any other **Design Wins** concept RISC-V based **Open Source IP** "European **Start-ups** RedHat Use of RISC-V Open **Universities** of Open Source IP for **Design Wins** RISC-V" **Application Component Design**

R&D FID

(First Industrial Deploment)

**Exploitation**

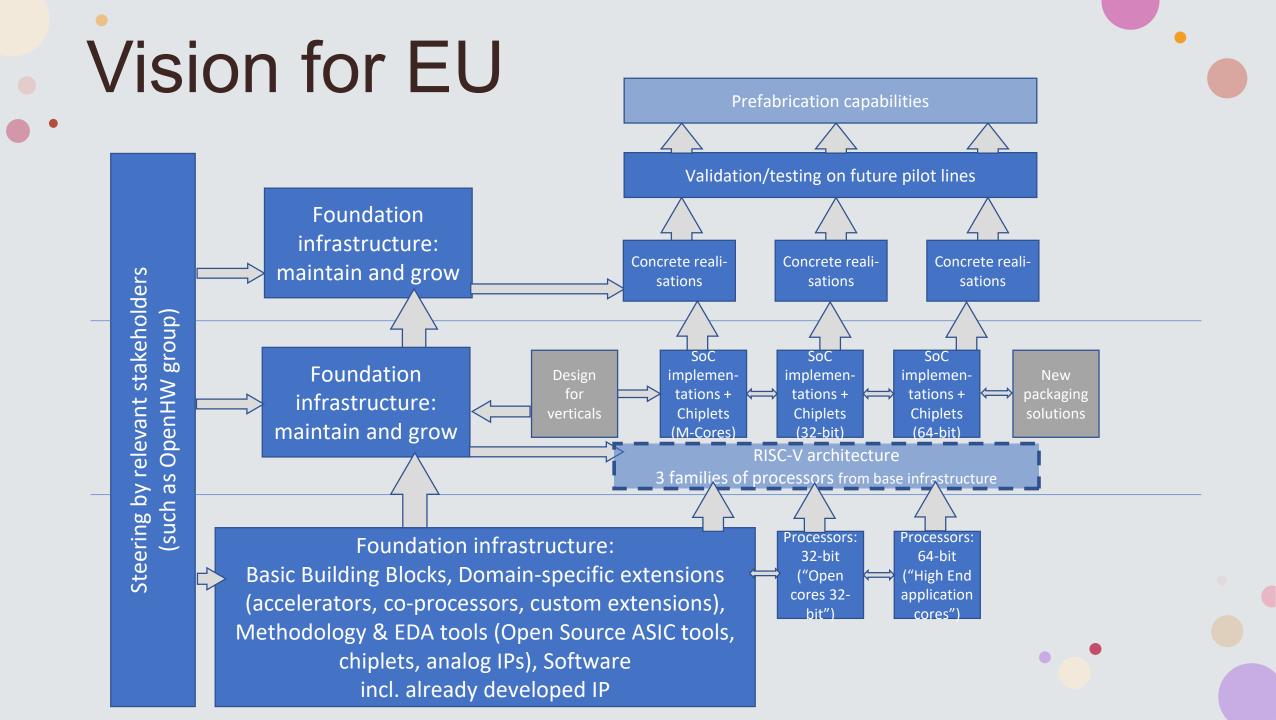

### How to realize the vision?

- Part of Phase 2 of the Working Group draft report available March 7<sup>th</sup>, 2022

- This report contains the following items:

- Value of RISC-V and Open Source IP and how to create business on the market, including business strategies, business models and licensing approaches

- Gaps and future needs for RISC-V and OpenSource IP

- Roadmap of Implementation Programs by means of Focus Topics

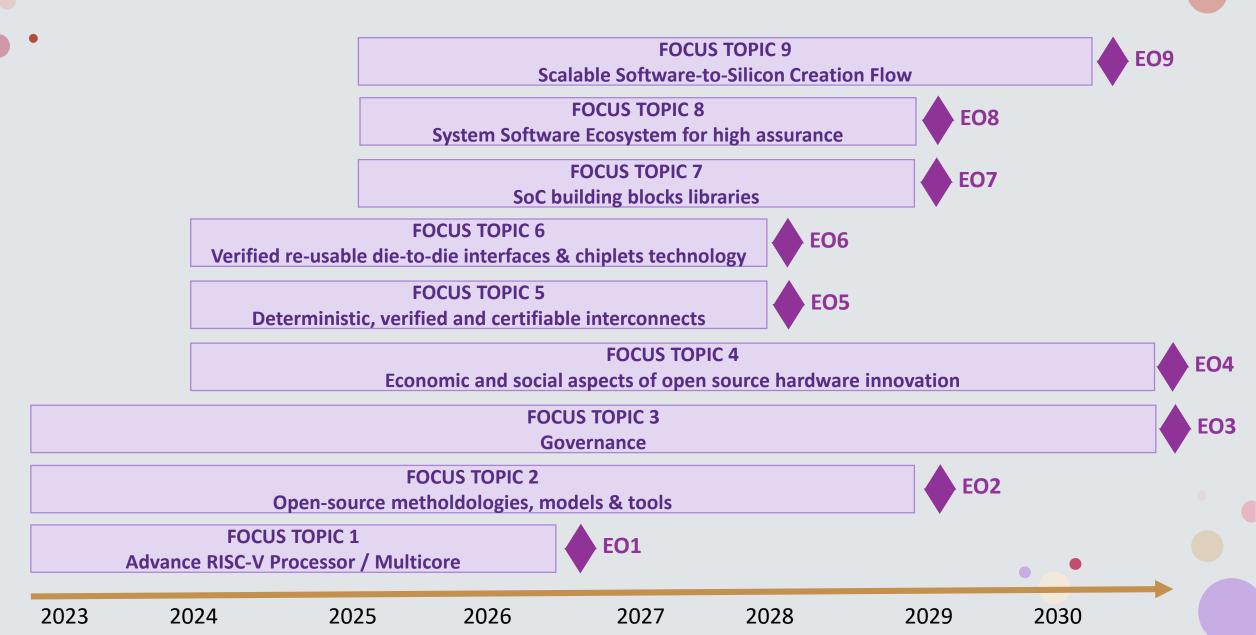

# Planning of Focus Topics & Expected Outcomes

# Conclusions & Next Steps

- Europe needs to act FAST

- F Firmly

- **A** Act

- S Strongly

- T Today

#### Next steps:

- Ensure enough RDI investments by all involved stakeholders ~ 1 Billion € program over 10 years

- Active involvement with and commitment from end-user companies

- Need for industrial leadership to get a professional European long term supported and maintained RISC-V based processor organization

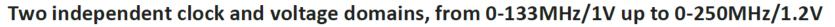

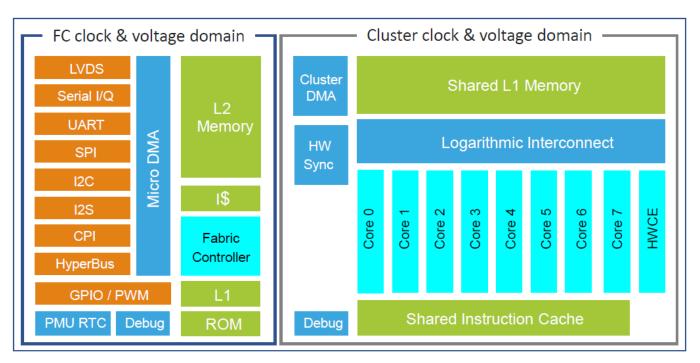

#### Let's build further upon EU Success Stories, e.g. GAP8 IoT processor

GREENWAVES TECHNOLOGIES

greenwaves-technologies.com